# ANALOG-TO-DIGITAL CONVERSION TECHNIQUES WITH THE M6800 MICROPROCESSOR SYSTEM

Prepared by:

Don Aldridge

Applications Engineering

This application note describes several analog-to-digital conversion systems implemented with the M6800 microprocessor and external linear and digital IC's. Systems consisting of an 8- and 10-bit successive approximation approach, as well as dual ramp techniques of 3½- and 4½-digit BCD and 12-bit binary, are shown with flow diagrams, source programs and hardware schematics. System tradeoffs of the various schemes and programs for binary-to-BCD and BCD-to-7 segment code are discussed.

MOTOROLA Semiconductor Products Inc.

# Analog-To-Digital Conversion Techniques with the M6800 Microprocessor System

#### INTRODUCTION

The MPU (microprocessing unit) is rapidly replacing both digital and analog circuitry in the industrial control environment. It provides a convenient and efficient method of handling data; controlling valves, motors and relays; and in general, supervising a complete processing machine. However, much of the information required by the MPU for the various computations necessary in the processing system may be available as analog input signals instead of digitally formatted data. These analog signals may be from a pressure transducer, thermistor or other type of sensor. Therefore, for analog data an A/D (analog-to-digital) converter must be added to the MPU system.

Although there are various methods of A/D conversion, each system can usually be divided into two sections — an analog subsystem containing the various analog functions for the A/D and a digital subsystem containing the digital functions. To add an A/D to the MPU, both of the sections may be added externally to the microprocessor in the form of a PC card, hybrid module or monolithic chip. However, only the analog subsystem of the A/D need be added to the microprocessor, since by adding a few instructions to the software, the MPU can perform the function of the digital section of the A/D converter in addition to its other tasks. Therefore, a system design that already contains an MPU and requires analog information needs only one or two additional inexpensive analog components to provide the A/D. The microprocessor software can control the analog section of the A/D, determine the digital value of the analog input from the analog section, and perform various calculations with the resulting data. In addition, the MPU can control several analog A/D sections in a timeshare mode, thus multiplexing the analog information at a digital level.

Using the MPU to perform the tasks of the digital section provides a lower cost approach to the A/D function than adding a complete A/D external to the MPU. The information presented in this note describes this technique as applied to both successive approximation (SA) A/D and dual ramp A/D. With the addition of a DAC (digital-to-analog converter), a couple of operational amplifiers, and the appropriate MPU software, an 8- or 10-bit successive approximation A/D is available. Expansion to greater accuracies is possible by modifying the

software and adding the appropriate D/A converter. The technique of successive approximation A/D provides medium speed with accuracies compatible with many systems. The second technique adds an MC1405 dual ramp analog subsystem to the MPU system and, if desired, a digital display to produce a 12-15 bit binary or a 3½- or 4½-digit BCD A/D conversion with 7-segment display readout. This A/D technique has a relatively slow conversion rate but produces a converter of very high accuracy. In addition to the longer conversion time, the MPU must be totally devoted to the A/D function during the conversion period. However, if maximum speed is not required this technique of A/D allows an inexpensive and practical method of handling analog information.

Figure 1 shows the relative merits of each A/D conversion technique. Listed in this table are conversion time, accuracy and whether interrupts to the MPU are allowed during the conversion cycle.

This note describes each method listed in Figure 1 and provides the MPU software and external system hardware schematics along with an explanation of the basic A/D technique and system peculiarities. In addition, the MPU interface connections for the external A/D hardware schemes are shown. These schemes are a complete 8-bit successive approximation and a 3½-digit dual ramp A/D system, both of which externally perform the conversion and transfer the digital data into the MPU system through a PIA.

For additional information on the MC6800 MPU system or A/D systems, the appropriate data sheets or other available literature should be consulted.

#### **MPU**

The Motorola microprocessor system devices used are the MC6800 MPU, MCM6810 RAM, MCM6830 ROM and MC6820 PIA (peripheral interface adapter). The following is a brief description of the basic MPU system as it pertains to the A/D systems presented later in this application note.

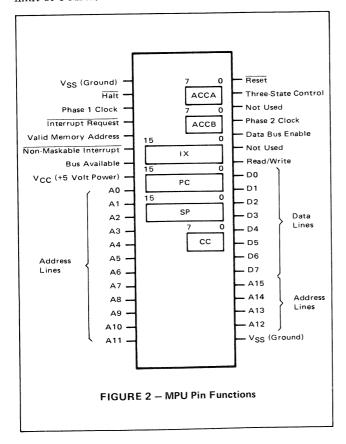

The Motorola MPU system uses a 16-bit address bus and an 8-bit data bus. The 16-bit address bus provides 65,536 possible memory locations which may be either storage devices (RAM, ROM, etc.) or interface devices (PIA, etc.). The basic MPU contains two 8-bit accumulators, one 16-bit index register, a 16-bit program counter, a 16-bit stack pointer, and an 8-bit condition code register. The condition code register indicates carry, half carry, interrupt, zero, minus, and 2's complement overflow. Figure 2 shows a functional block of the MC6800 MPU.

The MPU uses 72 instructions with six addressing modes which provide 197 different operations in the MPU. A summary of each instruction and function with the appropriate addressing mode is shown in Appendix A of this note.

Circuit diagrams external to Motorola products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this Application Note has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others.

|                                                                   | Succe                             | ssive Approxi                      | mation                                              |                             | Dual                       | Ramp                        |                                                               |

|-------------------------------------------------------------------|-----------------------------------|------------------------------------|-----------------------------------------------------|-----------------------------|----------------------------|-----------------------------|---------------------------------------------------------------|

| Characteristic                                                    | 8-Bit<br>Software                 | 10-Bit<br>Software                 | 8-Bit<br>Hardware                                   | 12-Bit<br>Software          | 3½-Digit<br>Software       | 4½-Digit<br>Software        | 3½-Digit<br>Hardware                                          |

| External Hardware                                                 | 8-Bit DAC<br>Op Amp<br>Comparator | 10-Bit DAC<br>Op Amp<br>Comparator | 8-Bit DAC<br>SAR*<br>Op Amp<br>Comparator           | MC1 <b>40</b> 5             | MC1405                     | MC1405                      | MC1405<br>MC14435<br>MC14558<br>(for 7-segment<br>display)    |

| Conversion Rate                                                   | 700 µs<br>Constant                | 1.25 ms<br>Constant                | 60 µs<br>for MPU,<br>plus A/D<br>Conversion<br>Time | 165 ms<br>(max)<br>Variable | 60 ms<br>(max)<br>Variable | 600 ms<br>(max)<br>Variable | 183 µs<br>(min) for<br>MPU, plus<br>A/D<br>Conversion<br>Time |

| Interrupt Capability                                              | Allowed                           | Allowed                            | Allowed                                             | Not<br>Allowed              | Not<br>Allowed             | Not<br>Allowed              | Allowed                                                       |

| Number of Memory Locations Required (Including PIA Configuration) | 106                               | 145                                | 42                                                  | 84                          | 296                        | 328                         | 58                                                            |

| Serial Output Available                                           | Yes                               | Yes                                | Yes                                                 | No                          | No                         | No                          | No                                                            |

<sup>\*</sup>Successive Approximation Register

FIGURE 1 — Relative Merits of A/D Conversion Techniques

The RAMs used in the system are static and contain 128 8-bit words for scratch pad memory while the ROM is mask programmable and contains 1024 8-bit words. The ROM and RAM, along with the remainder of the MPU system components, operate from a single +5 volt power supply; the address bus, data bus and PIAs are TTL compatible.

The MPU system requires a  $2\phi$  non-overlapping clock with a lower frequency limit of 100 kHz and an upper limit of 1 MHz.

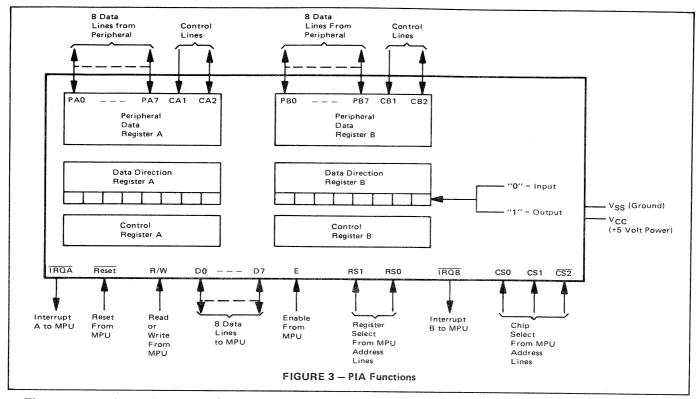

The PIA is the interface device used between the address and data buses and the analog sections of the A/D. Each PIA contains two essentially identical 8-bit interface ports. These ports (A side, B side) each contain three internal registers that include the data register which is the interface from the data bus to the A/D, the data direction register which programs each of the eight lines of the data register as either an input or an output, and the control register which, in addition to other functions, switches the data bus between the data register and the data direction register. Each port to the PIA contains two addition pins, CA1 and CA2, for interrupt capability and extra I/O lines. The functions of these lines are programmable with the remaining bits in the control register. Figure 3 shows a functional block of the MC6820 PIA.

Each PIA requires four address locations in memory. Two addresses access either of the two (A or B sides) data/data direction registers while the remaining two addresses access either of the two control registers. These addresses are decoded by the chip select and register select lines of the PIA which are connected to the MPU address bus. Selection between the data register and data direction register is made by programming a "1" or "0" in the third least significant bit of each control register. A logic "0" accesses the data direction register while a logic "1" accesses the data register.

By programming "0"s in the data direction register each corresponding line performs as an input, while "1"s in the data direction register make corresponding lines act as outputs. The eight lines may be intermixed between inputs and outputs by programming different combinations of "1"s and "0"s into the data direction register. At the beginning of the program the I/O configuration is programmed into the data direction register, after which the control register is programmed to select the data register for I/O operation.

The printouts shown for each A/D program are the source instructions for the cross assembler from the Motorola timeshare. Since the MPU contains a 16-bit address bus and an 8-bit data bus, the hexadecimal number system provides a convenient representation of these numbers. Although the assembler output is in hexadecimal, the source input may be either binary, octal, decimal or hexadecimal. A dollar sign (\$) preceding a number in the source instructions indicates hexadecimal, a percent sign (%) indicates binary and an at sign (@) indicates octal. No prefix indicates the decimal number system.

Only the beginning addresses of the program and labels are shown in the source programs. These beginning addresses may be changed prior to assembling the total system program or the programs may be relocated after assembly with little or no modification.

## SUCCESSIVE APPROXIMATION TECHNIQUES General

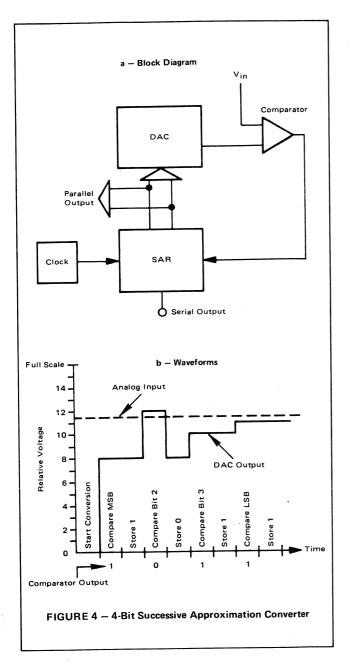

One of the more popular methods of A/D conversion is that of successive approximation. This technique uses a DAC (digital-to-analog converter) in a feedback loop to generate a known analog signal to which the unknown analog input is compared. In addition to medium speed conversion rates, it has the advantages of providing not only a parallel digital output after the conversion is completed but also the serial output during the conversion.

Figure 4 shows the block diagram and waveform of the SA-A/D. The DAC inputs are controlled by the successive approximation register (SAR) which is, as presented here, the microprocessor. The DAC output is compared to the analog input  $(V_{in})$  by the analog comparator and its output controls the SAR. At the start of a conversion

the MSB of the DAC is turned on by the SAR, producing an output from the DAC equal to half of the full scale value. This output is compared to the analog input and if the DAC output is greater than the input unknown, the SAR turns the MSB off. However, if the DAC output is less than the input unknown, the MSB remains on. Following the trial of the MSB the next most significant bit is turned on and again the comparison is made between the DAC output and the input unknown. The same criteria exists as before and this bit is either left on or turned off. This procedure of testing each bit continues for the total number of DAC inputs (bits) in the system.

After the comparison of each bit the digital output is available immediately thus providing both the serial output as well as the parallel output at the end of the conversion. The serial output provides the MSB first, followed by the remaining bits in order. The total conversion time for the SA-A/D is the time required to turn on a bit, compare the DAC output with the input unknown and, if required, turn the bit off, multiplied by the total number of bits in the A/D system. The conversion time is hence constant and unaffected by the analog input value.

One SA-A/D shown in this note uses an 8-bit DAC (MC1408) to produce an 8-bit A/D; a second version uses a 10-bit DAC (MC3410)\* to produce a 10-bit A/D. Both of these are used in conjunction with the MPU as an SAR. In addition, the MC1408 is shown with the MC14549 CMOS SAR as a convert-on-command system under control of the MPU. All of these A/Ds produce a binary output. However, by adding the appropriate software a BCD output or 7-segment-display outputs are available. Also by using a BCD-weighted DAC, the BCD output can be produced directly.

#### 8-Bit SA Program

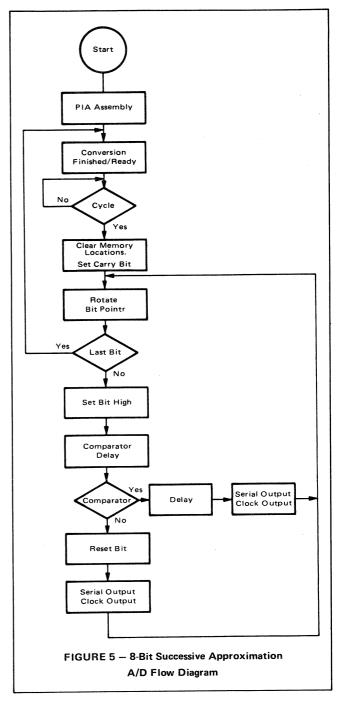

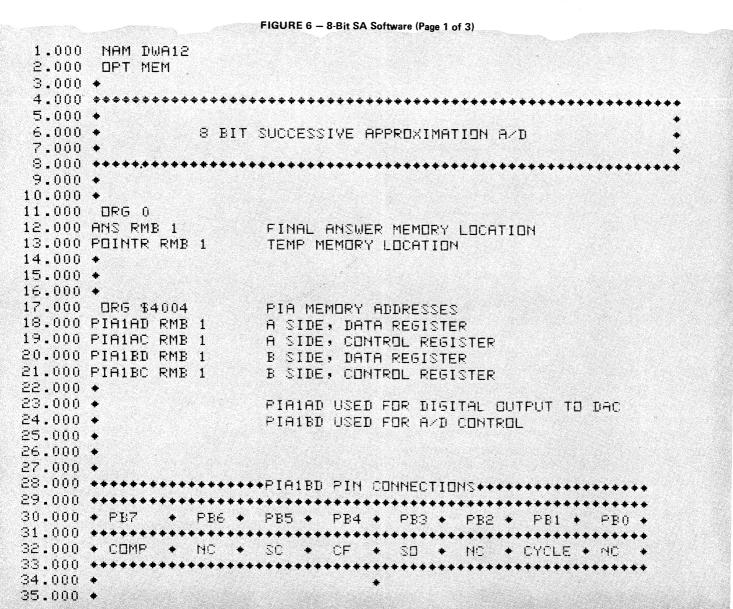

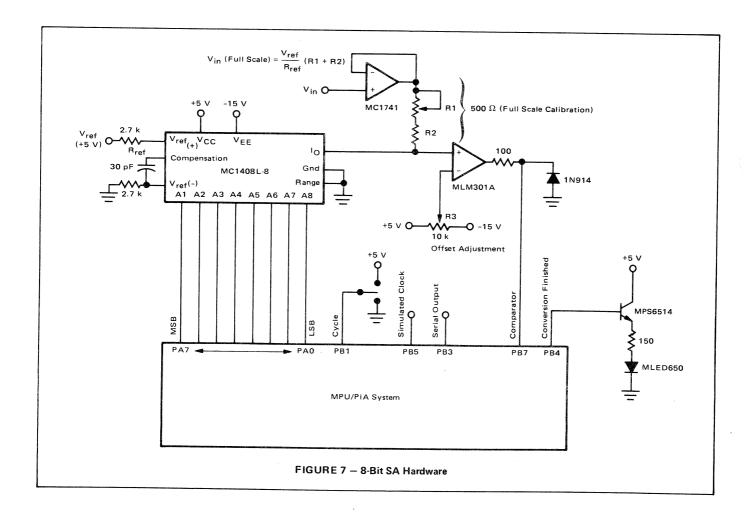

The flow chart for the 8-bit MPU A/D system is shown in Figure 5; Figures 6 and 7 show the software and the hardware external to the microprocessor. The DAC used is the MC1408L-8 which has active high inputs and a current sink output. An uncompensated MLM301A operational amplifier is used as a comparator while an externally compensated MLM301A or internally compensated MC1741 operational amplifier is used as a buffer amplifier for the input voltage. The output voltage compliance of the DAC is ±0.5 volt; if the current required by the D/A does not match that produced from the output of the buffer amplifier through R1 and R2, then the DAC output will saturate at 0.5 volt above or below ground, thus toggling the comparator. The system is calibrated by adjusting R1 for 1 volt full scale, and zero calibration is set by adjusting R3.

The first MPU instruction for the 8-bit A/D is in line 45 of Figure 6. After assembly, this instruction will be placed in memory location \$0A00 as defined in the assembler directive of line 42. The assembled code for this program is relocatable in memory as long as the PIA addresses and storage addresses are unchanged. The program as shown requires 106 memory bytes. Source program lines 45 through 53 configure the PIAs for the proper input/output configuration. PIA1BD is used for various control functions between the MPU system and the external hardware. The exact configuration of this PIA is shown in lines 28 through 33 of Figure 6. PIA1AD provides the 8-bit output needed for the DAC. Lines 51 through 53 set bit 3 of the PIA control register to access the data register for the actual A/D program.

Lines 55 and 56 set the conversion finished flag, which consists of a LED on the hardware schematic, after which the program enters a loop in lines 63-65 which causes the MPU to wait until the cycle input line goes high. (This feature could be eliminated if the program was a subroutine of a larger control program.) In this case, when a conversion was to be made the control program would go to the A/D subroutine and return with the digital results. Lines 68 and 69 clear the PIA-A which is connected to the DAC inputs and an internal memory location. This memory location is used as a pointer to keep track of which bit of the DAC is currently being tested. Next the conversion finished line is reset indicating a conversion is in process and the carry bit of the condition code register is set. The memory location POINTR is then rotated right in line 79, moving the carry bit of the condition code register into the MSB of that memory location. Line 80 is a conditional branch that determines if all 8 bits of the DAC have been tested. After nine rotations of POINTR the carry bit will again be set indicating all 8 bits have been compared.

Program lines 81 through 83 load the previous DAC value into an accumulator and the next DAC bit is turned on for the comparator test. An 8  $\mu$ s delay produced by

the NOP instruction of lines 87 through 90 allows the DAC and comparator to settle to a final value before the comparator test of lines 91 and 92. At this point if the comparator was high the Yes loop is executed, which generates a simulated clock pulse and a serial output "1". If the comparator was low, lines 95 through 101 are executed, resetting the bit under test and generating a simulated clock pulse and a serial output of "0". The three NOP instructions of the Yes loop equalize the execution time between the high and low comparator loops. After completion of either the high or low comparator loop, the A accumulator which contains the new digital number is stored in PIA1AD and in a RAM memory location labeled ANS. Then the next bit of the DAC is tested in the same manner and this procedure is continued until all eight DAC inputs have been tested. When this has occurred the program returns to line 55 where the conversion finished flag is "set" and the MPU awaits the next cycle input from PIA1BD.

The total conversion time is 700  $\mu$ s for the 8-bit converter assuming a 1 MHz MPU clock frequency. The simulated clock pulse is 7  $\mu$ s wide and can be used to indicate when to sample the serial output.

```

36.000 *

37.000 ◆ COMP-COMPARATOR,SC-SIMULATED CLOCK,SO-SERIAL DUTPUT

38.000 ◆ CF-CONVERSION FINISHED, NC-NO CONNECTION

39.000 *

40.000 *

41.000 *

BEGINNING ADDRESS

42.000 DRG $0A00

43.000 +

**PIA ASSEMBLY**

44.000 +

45.000 CLR PIAIAC

46.000 CLR PIA1BC

47.000 LDA A $$7C

48.000 STA A PIA1BD

49.000 LDA A $∄0FF

50.000 STA A PIA1AD

A SIDE ALL DUTPUTS

51.000 LDA A $$04

52.000 STA A PIA1AC

53.000 STA A PIA1BC

54.000 +

55.000 RSTART LDA A #$10

56.000 STA A PIA1BD SET CONVERSION FINISHED

57.000 +

58.000 *

59.000 +

**CYCLE TEST**

60.000 *

61.000 *

62.000 +

63.000 CYCLE LDA A PIAIBD

64.000 AMD A #$02

65.000 BEQ CYCLE

66.000 +

67.000 +

68.000 CLR PIA1AD

69.000 CLR PDINTR

70.000 *

71.000 +

72.000 *

RESET CONVERSION FINISHED

73.000 CLR PIA1BD

74.000 SEC

75.000 +

76.000 +

77.000 *

78.000 *

79.000 CONVET ROR POINTR

80.000 BCS RSTART

RECALL PREVIOUS DIGITAL DUTPUT

81.000 LDA A PIA1AD

82.000 ADD A POINTR

SET NEW DIGITAL DUTPUT

83.000 STA A PIAIAD

84.000 +

**DELAY FOR COMPARATOR**

85.000 +

86.000 *

87.000 MOP

88.000 MOP

89.000 HDP

90.000

HOP

LDA A PIA1BD COMPARATOR TEST

91.000

BMI YES

92.000

93.000 +

**LOW COMPARATOR LOOP**

94.000 *

95.000 LDA A PIA1AD

```

7

96.000 SUB A POINTR

```

97.000

LDA B #$20

SERIAL DUT OF "O", CLOCK SET

98.000

STA B PIA1BD

99.000

CLR B

CLOCK RESET

100.000

STA B PIA1BD

101.000

BRA END

102.000 *

103.000 +

**HIGH COMPARATOR LOOP**

104.000 YES LDA A PIA1AD

105.000

MOP

106.000

HOP

DELAY

107.000

MOP

108.000

LDA B #$28

SERIAL DUTPUT OF "1", CLOCK SET

109.000

STA B PIA1BD

110.000

LDA B #$08

CLOCK RESET

111.000 STA B PIA1BD

112.000 *

113.000 END STA A PIAIAD

114.000 STA A ANS

115.000 BRA CONVRT

116.000 *

117.000 +

118.000 *

119.000 *

120.000 *

121.000 +

122.000 MDN

```

FIGURE 6 - 8-Bit SA Software (Page 3 of 3)

#### 10-Bit SA Program

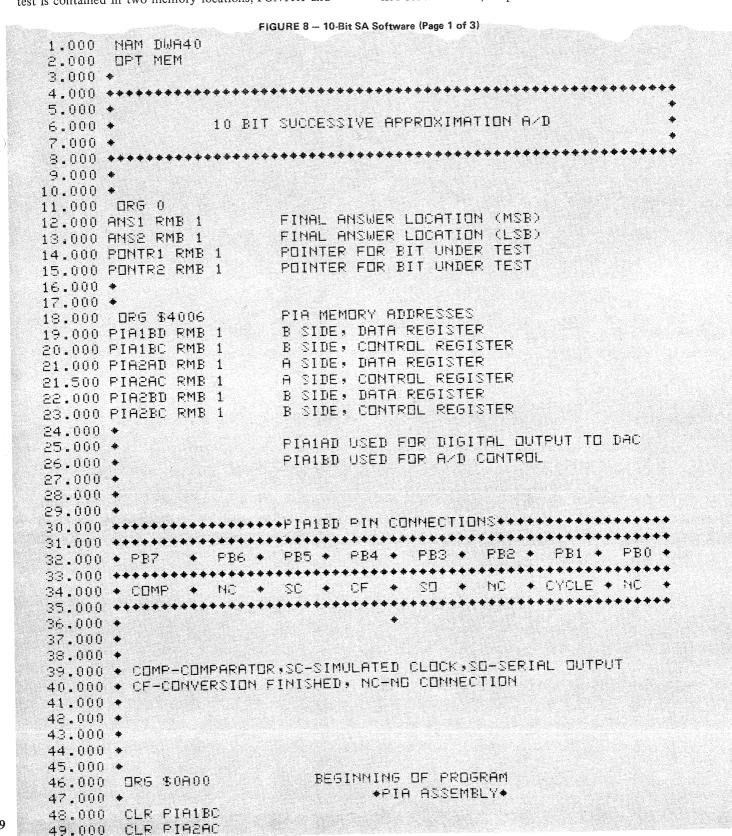

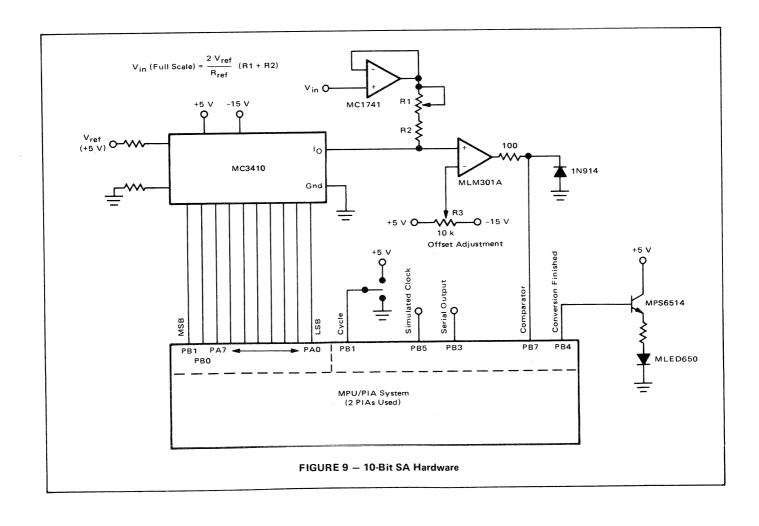

Figures 8 and 9 show the MPU software and external hardware for a 10-bit successive approximation A/D using the MC3410 DAC. The operation of this A/D is very similar to that of the 8-bit A/D. Both the A and B halves of a PIA are required for the DAC output while the control lines (comparator, conversion finished, etc.) are also identical to that of the 8-bit A/D previously discussed. The pointer for indicating which bit is currently under test is contained in two memory locations, PONTR1 and PONTR2. The pointer is initialized in lines 63 and 64 and as before, it is continuously shifted to the left as each bit is tested. Lines 72 through 77 and lines 89 through 101 operate on both halves of the PIA, "setting" and "resetting" the DAC bits under test. The final answer is stored in the two PIA memory locations as well as two internal memory locations (ANS1 and ANS2).

By using the appropriate DAC and changing line 63 of the software program, the 10-bit SA D/A can be modified for 9-16 bit A/D operation.

```

SUB A PONTR2

113.000

114.000

STA A PIASBD

STA A ANS2

115.000

SERIAL DUTPUT (CLOCK DNLY)

LDA B #$20

116.000

STA B PIAIBD

117.000

CLOCK RESET

118.000

CLR B

STA B PIA1BD

119.000

BRA END

120.000

121.000 *

122.000 *

*HIGH COMPARATOR LOOP*

123.000 *

TIME EQUALIZATION

124.000 YES LDA A #$05

125.000 DELAY DEC A

BNE DELAY

126.000

SERIAL DUTPUT

127.000

LDA B #$28

STA B PIAIBD

128.000

CLOCK RESET

LDA B #$08

129.000

STA B PIA1BD

130.000

131.000

HOP

132.000 NDP

133.000 *

134.000 END BRA CONVRT

135.000 *

136.000 +

137.000 *

138.000 M□N

```

FIGURE 8 - 10-Bit SA Software (Page 3 of 3)

#### **External SA System**

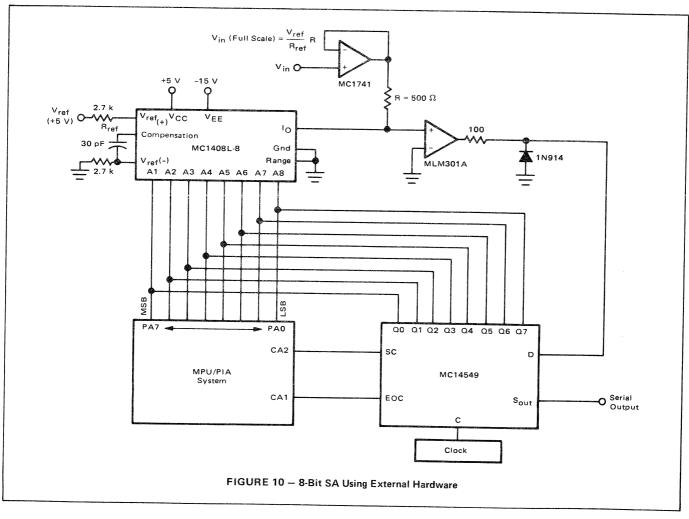

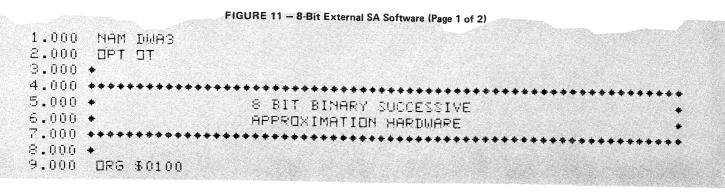

The third successive approximation program, shown in Figures 10 and 11, uses an MC1408 DAC with the MC14549 CMOS SAR for a convert-on-command A/D system. This system is controlled by the MPU through the CA1 and CA2 PIA pins to start a conversion and store the results of this conversion in memory when the conversion is finished. The 8-bit data word from the A/D is brought in to the MPU system through PIA1AD. The advantages of this A/D system are that a minimum number of software instructions are required, a higher speed conversion is possible, and the MPU may be performing other tasks during the conversion. The disadvantage is a higher parts count and increased cost.

The program for this A/D, shown in Figure 11, is written as a subroutine of a larger program. This larger program is simulated with the instructions of lines 28

through 31. The subroutine starts in line 34, unmasking the interrupt input on CA1 and setting CA2 high. (For additional information on use of the CA1 and CA2 lines, see the MC6820 data sheet.) CA2 initiates the conversion. Line 35 is a dummy read statement necessary to clear the data register of the interrupt bit associated with the CA1 input line. Then a wait for interrupt instruction stores the stack in anticipation of the A/D conversion being completed. When the conversion is finished the CA1 line is toggled by the EOC output of the MC14549 and the program goes to line 43 where CA1 is masked and CA2 is set low, thus stopping any further conversion sequences by the A/D. The digital results are loaded into the A accumulator through PIA-A and stored in memory location TEMP. Then the MPU returns from the interrupt and finally returns from the subroutine.

The entire sequence requires 60  $\mu s$  plus the conversion time of the A/D.

12

```

8 BIT BINARY DATA

10.000 TEMP RMB 1

11.000

12.000 •

DRG $4004

13.000

DATA REGISTER

14.000 PIA1AD RMB 1

CONTROL REGISTER

15.000 PIA1AC RMB 1

16.000 *

17.000 *

18.000 *

19.000 *

20.000

DRG $0300

PIA ASSEMBLY

CLR PIA1AC

21.000

CLR PIA1AD

22.000

LDA A #$30

23.000

STA A PIA1AC

24.000

LDS #$0020

25.000

26.000 *

27.000 *

28.000

MOP

JSR COMVRT

29.000

30.000 END MOP

31.000

BRA END

32,000 +

CONVERSION SUBROUTINE

33.000 *

CA1 UNMASKED, POS EDGE--CA2 HIGH

34.000 CONVRT LDA A #$3F

LDA B FIAIAD

35.000

STA A PIA1AC

36.000

37.000

WAI

38.000

RTS

39.000 *

40.000 *

41.000

INTERRUPT PROGRAM

42.000 +

43.000 INTRPT LDA A #$36

CA1 MASKED-CA2 LOW

STA A PIA1AC

44.000

LDA A PIAIAD

45.000

46.000

STA A TEMP

RTI

47.000

48.000 *

49.000 *

50.000 *

51.000 MON

```

FIGURE 11 - 8-Bit External SA Software (Page 2 of 2)

#### **DUAL RAMP TECHNIQUES**

#### General

Another commonly used method for A/D conversion is the dual ramp or dual slope technique. This approach has a longer conversion time than that of the successive approximation method. The conversion time period is also variable and input voltage dependent. However, this method yields an A/D converter of high accuracy and low cost.

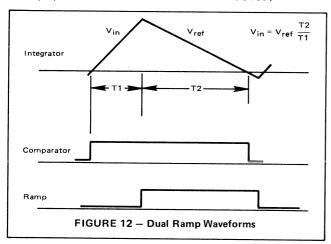

As the name implies the dual ramp method consists of two ramp periods for each conversion cycle. Figure 12 shows the basic waveforms for the dual ramp A/D. The

ratio in time of the ramp lengths provides a value representing the difference between a reference and an unknown voltage. During time period T1, the input unknown is integrated for a fixed time period (fixed number of clock cycles). The integrator voltage increases from the reference level to a voltage which is proportional to the input voltage. At the end of this time period a reference voltage is applied to the input of the integrator causing the integrator output voltage to decrease until the reference level is again reached. The number of clock cycles that are required to bring the integrator output voltage back to the reference level is proportional to the input unknown voltage.

The dual ramp converters discussed here use the MC1405 analog subsystem in conjunction with the M6800 MPU system. The MC1405 provides the integrator, comparator and reference voltage required for the analog functions of the dual ramp A/D. The analog device also adds an offset current to the integrator input during the ramp up time period to stabilize small voltage readings. The digital section of the A/D must subtract an equivalent number of counts to produce a zero reading display output for a zero input. The interface between the analog and digital subsystems consists of two control lines. These are the comparator output from the analog part, which indicates whether the ramp is above or below the reference level, and a ramp control output from the digital part to switch the integrator input between the input unknown voltage and the reference voltage. The control of these lines, offset subtraction, and calculations with the resulting data must be handled by the digital subsystem, which in this case is the MPU.

For additional information on the dual ramp technique for A/D, consult the data sheet for the MC1405.

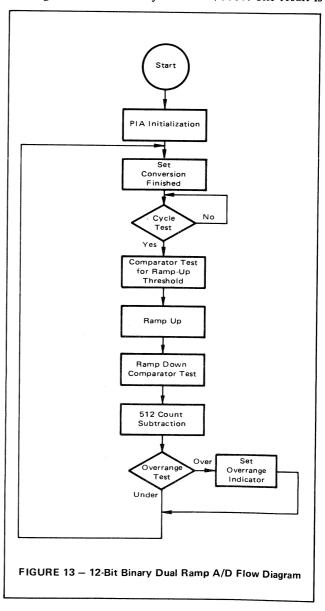

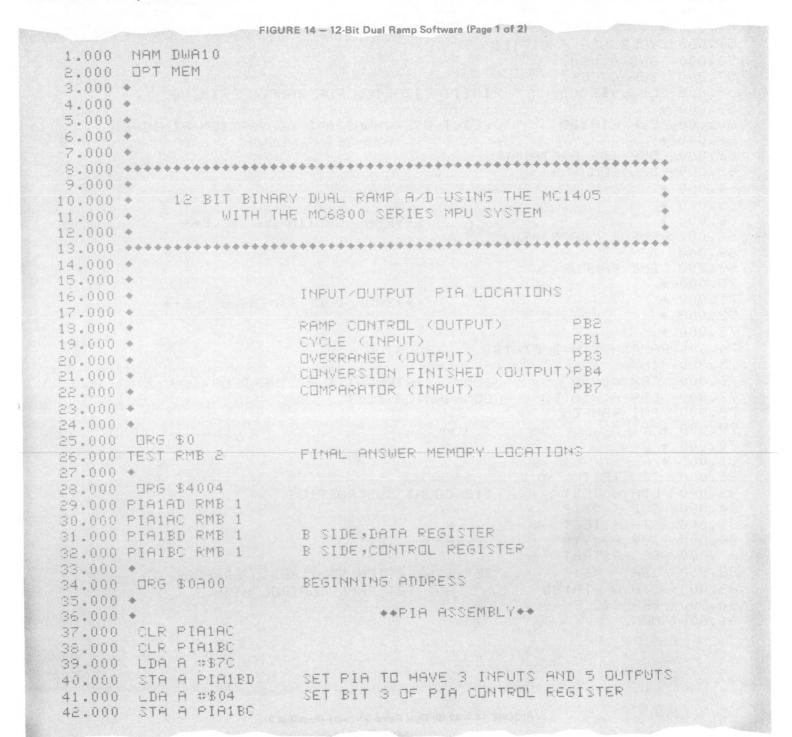

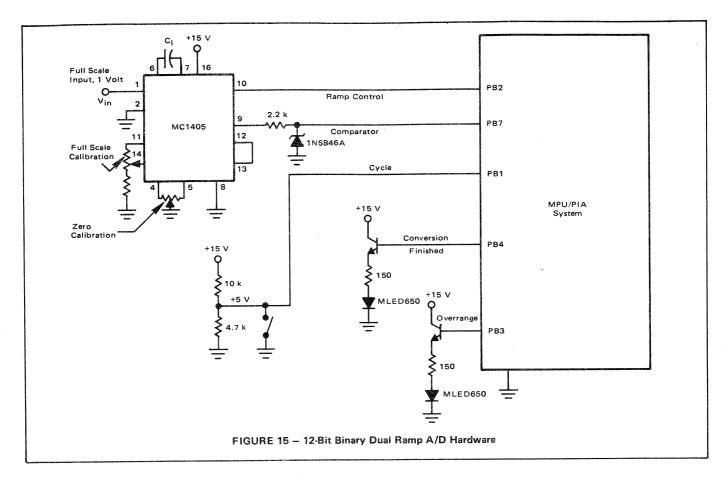

#### 12-Bit Dual Ramp Program

This version of the dual ramp A/D generates a 12-bit binary output from a 1 volt full scale analog input. Figures 13, 14 and 15 show the flow chart, MPU software and external hardware. The interface of the PIAs used for this A/D is shown both on the schematic and in lines 16 through 22 of the source program. Lines 25 and 26 indicate the two memory locations where the final 12-bit binary result is stored. These locations are \$0000 and \$0001. The four most significant bits are in location \$0000 while the remaining eight bits are in \$0001.

Referring to the software of Figure 14, the first instructions (lines 37 through 42) initialize the PIA for its input/output configuration. Source program lines 46 through 49 set the ramp control line of the MC1405 and check the comparator output from the MC1405 to insure that the integrator output is below the reference level at the start of a conversion. Next the "conversion finished" flag is set indicating a conversion ready status. Then the MPU enters a loop (lines 55 through 57) waiting for a cycle input (PB1) from the PIA. When this condition occurs the conversion finished flag is reset while the

ramp control line (PB2) goes low, thus starting a conversion cycle. In addition, the index register has been loaded with \$2000 which will be decremented to provide the ramp up timing period. When the ramp crosses the threshold level the comparator (PB7) change from low to high causes the MPU to enter the timing cycle of lines 67 through 69. The index register is continuously decremented until reaching zero, at which point the ramp control line (PB2) to the MC1405 is set high (line 74) and the index register is incremented (line 75). This loop continues until the integrator output again reaches the threshold level. Line 76 of the ramp down cycle is a dummy statement included to equalize the timing between the ramp up and ramp down time periods. The proper timing ratio (2:1 in this example) must be maintained for correct A/D operation.

After the termination of the ramp down time period the content of the index register is stored in memory locations \$0000 and \$0001 (line 82). Next the offset counts are subtracted (512<sub>10</sub>) from this result by subtracting \$01 from memory location \$0000. The result is

then stored back into the same memory location. Lines 86 and 87 check the contents of memory location TEST for a number greater than 4095<sub>10</sub>. If this condition occurs, the overrange, conversion finished, and ramp control bits are set high. Otherwise the MPU branches back to line 50 where only the conversion finished and ramp control bits are set high. The program then checks the status of the cycle input waiting for the next conversion.

When assembled, the first instruction will be located at \$0A00 with 8410 memory locations required. The full scale conversion time is 165 ms assuming a 1 MHz clock in the MPU system.

As with all MC1405 designs, the integration capacitor must be large enough to insure that the integrator does not saturate during the ramp up time period. The value of this capacitor depends upon the power supply voltage applied to the MC1405 and the ramp up time period. The MC1405 data sheet contains the equations for calculation of this capacitor. The MC1405 is capable of operating on a single +5 volt power supply; however, a +15 volt supply voltage is recommended to decrease the integrator capacitor size. When using 15 volts the comparator output must be clamped at 5 volts to prevent damaging the PIA inputs.

```

43.000 *

44.000 *

45.000 *

46.000 LDA A #$04

47.000 STA A PIAIBD

RAMP CONTROL HIGH

48.000 START LDA A PIAIBD COMPARATOR TEST - INSURES RAMP IS LOW

49.000 BMI START

TO START CONVERSION

50.000 RSTART LDA A #$14

51.000 STA A PIAIBD CONVERSION READY , RAMP CONTROL HIGH

52.000 *

53.000 +

54.000 *

**CYCLE TEST**

55.000 CYCLE LDA A PIAIBD

56.000

SOR# A UMA

57.000

BEQ CYCLE

58.000 LDX #$2000

INITIALIZATION FOR RAMP UP TIMING

59.000 *

60.000 CLR PIA1BD RESET OVERRANGE AND CONVERSION FINISHED

61.000 *

AND SET RO LOW

62.000 COMP LDA A PIAIRD

63.000 BPL COMP

64.000 +

65.000 *

66.000 *

**RAMP UP TIMING CYCLE**

67.000 RAMPUP LDA B #$04

68.000 DEX

69.000 BNE RAMPUP

70.000 *

71.000 *

**RAMP DOWN TIMING CYCLE**

72.000 *

73.000 *

74.000 RAMPDN STA B PIA1BD RC HIGH

75.000

INX

CPX #0000

76.000

DUMMY STATEMENT FOR TIME DELAY

77.000 LDA A PIA1BD

COMPARATOR TEST

78.000

BMI RAMPDN

79.000 *

80.000 *

81.000 *

82.000 STX TEST

83.000

LDA A TEST

512 COUNT SUBTRACTION

84.000

SUB A #$02

85.000

STA A TEST

86.000

OVERRAMSE TEST

SUB A #$10

87.000

BCS RSTART

88.000

LDA A ##1C

SET CONVERSION FINISHED JUVERRANGE

89.000

STA A PIA1BD

AND SET RAMP CONTROL HIGH

90.000 BRA CYCLE

91.000

MOM

```

FIGURE 14 - 12-Bit Dual Ramp Software (Page 2 of 2)

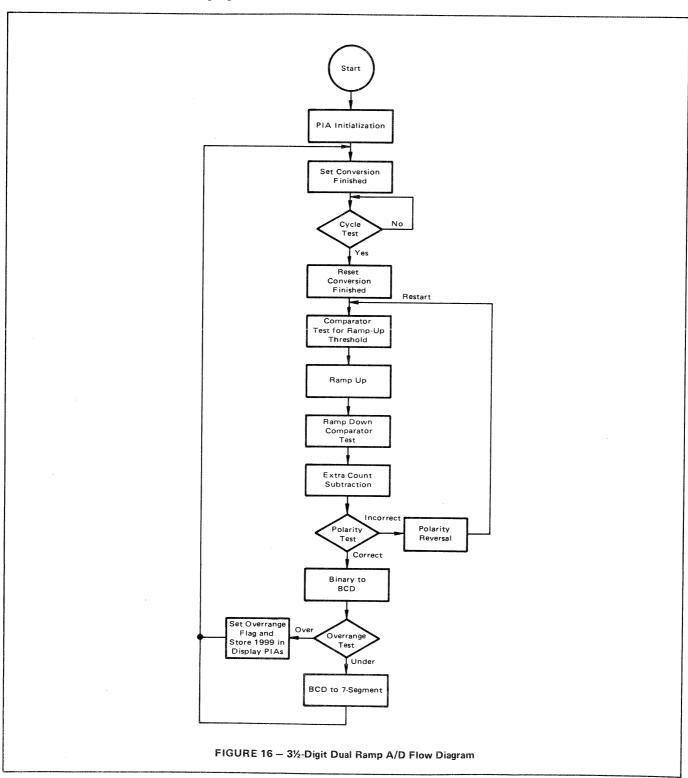

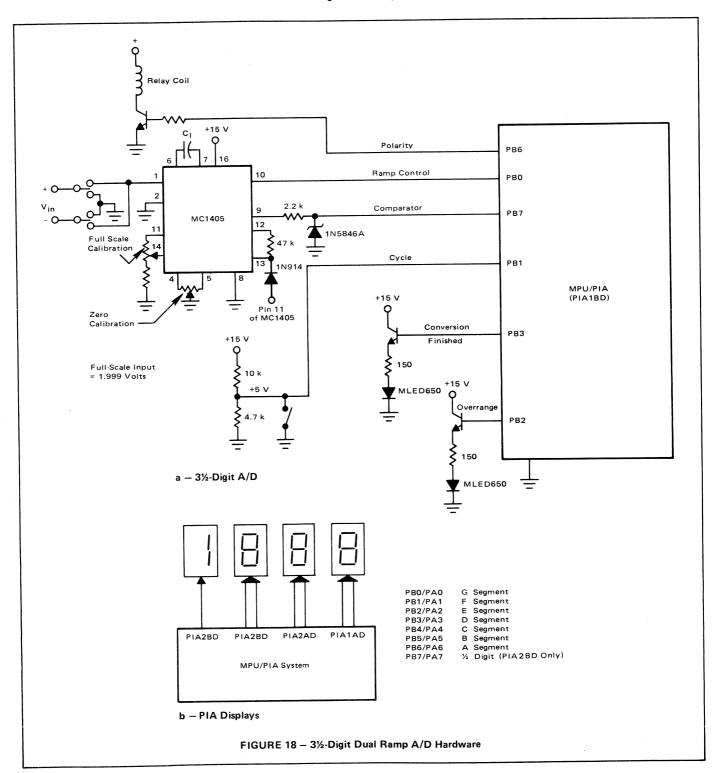

#### 3½-Digit Dual Ramp Program

The flow chart, source program and hardware for a 31/2-digit system are shown in Figures 16, 17, and 18 respectively. Referring to Figure 17, the basic conversion routine of lines 96 through 135 in this program is similar to that of the previously discussed 12-bit binary system. The initialization of the index register in line 108 has been changed to increase the ramp up time period. The basic conversion results in a binary number as did the 12-bit version previously discussed. This binary result is converted by the software routine in lines 144 through 180 to produce 3½-digit BCD output. This routine converts up to a 16-bit binary number to the equivalent BCD value. Also the BCD result is converted to a 7-segment display code for use in a LED or LCD readout system. Another feature of the 3½-digit A/D program shown here is a polarity detection scheme. This allows the A/D to handle both positive and negative input voltages.

The external hardware for the 3½-digit A/D requires two full PIAs; one of the four ports is used for interface to the MC1405, cycle input, overrange flag, etc. An I/O configuration similar to that of the 12-bit binary A/D is used. The remaining three ports of the PIAs are used for the 3½-digit display, as shown in Figure 18b.

The conversion initially produces a binary result which is stored in memory locations MSB and MSB+1. This result has  $100_{10}$  offset counts subtracted, and then a polarity check is made. If the polarity that is currently being applied to the input of the MC1405 is positive, the

binary number is converted to a BCD number. The technique used for binary-to-BCD conversion is described in Appendix B. The BCD results are stored in memory locations UNTTEN and HNDTHD. Each of these memory locations contains two BCD words. Following the conversion, an overrange test is made in lines 183 through 186 which checks for a maximum of a BCD "1" in the upper four bits of memory location HNDTHD. If an overrange condition occurs, the program branches to lines 227 through 234 where a 1999<sub>10</sub> is placed in the display and the overrange flag in PIA1BD is "set".

After the overrange test the BCD code is converted to a 7-segment code and stored in the memory location for each PIA port. Segments A through G use PIA outputs 0 through 6 while the half digit output uses PIA2BD output PB7. The conversion technique for BCD-to-7 segment utilizes a look-up table in line 251 with the indexed mode of addressing to access the table. Each of the three full BCD digits is converted to the 7-segment code by first separating the lower BCD and upper BCD word and using the BCD code as the least significant byte of a two byte address for the look-up table. This address is then loaded into the index register and used to locate the corresponding 7-segment code. In the case of the upper BCD digit of each BCD, the memory must be shifted left four times for correct addressing of the look-up table. Finally, the half digit output is added to PIA2BD in lines 197 through 226.

Should the MC1405 have the incorrect polarity on its input, a polarity reversing relay is operated by toggling the

CA2 output of PIA1BC control register. Then the conversion is restarted, this time with a positive input polarity. The polarity detection instruction is found in line 131. If after the offset count subtraction in lines 129 and 130 the condition code carry bit is "set", the MC1405 has a negative input voltage. This occurs when the negative input subtracts from instead of adding to the offset current in the MC1405 and does not allow the ramp down time period to reach at least a value of 10010 counts. If the carry bit has been "set" then the program branches to

line 236 where the CA2 line is toggled. Also due to the difference in a positive polarity conversion and a negative polarity conversion a short delay loop has been added in lines 238 and 239 to improve accuracy at very small input voltages.

The entire 3½-digit A/D requires 296 memory locations but can be reduced if the BCD-to-7 segment decoding is performed external to the MPU system. With a 1 MHz MPU clock frequency this program has a full scale conversion time of 60 ms.

A SIDE DATA REGISTER

59.000 ORG \$4004

60.000 PIA1AD RMB 1

19

```

FIGURE 17 - 3½-Digit Dual Ramp Software (Page 2 of 5)

61.000 PIA1AC RMB 1

A SIDE CONTROL REGISTER

62.000 FIA1BD RMB 1

B SIDE DATA REGISTER

63.000 PIA1BC RMB 1

B SIDE CONTROL REGISTER

64.000 PIA2AD RMB 1

A SIDE DATA REGISTER

65.000 PIA2AC RMB 1

A SIDE CONTROL REGISTER

66.000 PIASBD RMB 1

B SIDE DATA REGISTER

67.000 PIA2BC RMB 1

B SIDE CONTROL REGISTER

68.000 *

69.000 +

70.000 DRG $0A00

71.000 •

72.000 *

**PIA ASSEMBLY**

73.000

CLR PIA1AC

74.000

CLR PIA1BC

75.000

CLR PIASAC

76.000

CLR PIASBC

77.000

LDA A #$70

78.000

STA A PIA1BD

79.000

LDA A ##OFF

80.000

STA A PIA1AD

81.000

STA A PIASAD

82.000

STA A PIASBD

83.000 LDA A #$34

SETS PIA CONTROL REGISTER BIT 3 HIGH

84.000

STA A PIA1AC

85.000

STA A PIA1BC

86.000

STA A PIASAC

87.000 STA A PIA2BC

88.000 .

89.000 LDA A $$0C

FIRST TWO HEX DIGITS OF LOOK-UP

90.000 STA A INDEX

TABLE ADDRESSES

91.000 +

92.000 *

BASIC A/D *

93.000 +

*****

94.000 *

95.000 *

INITIALIZATION

96.000 LDA A $$04

97.000 STA A PIAIRD RC HIGH

98.000 START LDA A PIAIBD COMPARATOR TEST

99.000 BMI START

100.000 CYCLE1 LDA A #314

101.000 STA A PIAIBD CONVERSION READY AND RC HIGH

102.000 *

103.000 *

104.000 *

**CYCLE TEST**

105.000 CYCLE LDA A PIA1BD

106.000 AND A #$02

107.000 BED CYCLE

108.000 RESTAR LDX #$07D0

109.000 CLR PIA1BD RESET OVERRANGE: CONVERSION FINISHED AND SET RC LOW

110.000 COMP LDA A PIA1BD

111.000 BPL COMP

112.000 +

**RAMP UP TIMING CYCLE**

113.000 RAMPUP LDA B #$04

114.000 DEX

115.000 BNE RAMPUP

116.000 *

117.000 *

**RAMP DOWN TIMING CYCLE**

118.000 *

119.000 *

120.000 RAMPDN STA B PIA1BD RC HIGH

```

20

```

121.000 INX

DUMMY STATEMENT FOR TIME DELAY

122.000 CPX #0000

123.000 LDA A PIAIBD COMPARATOR TEST

124.000 BMI RAMPIN

125.000 *

126.000 STX MSB

LDA A MSB+1

127.000

LDA B MSB

128.000

129.000 SUB A ≎$64

SBC B #$00

130.000

BCS POLRY1

131.000

STA A MSB+1

132.000

133.000 STA B MSB

134.000 STA A MSBTEM+1

135.000 STA B MSBTEM

136.000 *

137.000 *

138.000 +

139.000 *

* BIMARY TO BCD *

140.000 *

CONVERTER

141.000 *

142.000 *

143.000 *

144.000 CLR UNTTEN

145.000 CLR HNDTHD

146.000 LDX $$0010

147.000 BEGIN LDA A UNTTEN

148.000 TAB

AND A #BOF

149.000

150.000 SUB A #$05

BMI AT

151.000

152.000 ADD B $$03

153.000 AT TBA

AMD A #$OFO

154.000

155.000 SUB A ≎$50

156.000 BMI BT

ADD B #$30

157.000

158.000 BT STA B UNTIEN

159.000 *

160.000 LDA A HNDTHD

161.000 TAB

AND A #80F

162.000

SUB A #805

163.000

164.000 BMI CT

165.000 ADD B #$03

166.000 CT TBA

167.000 AND A #$0F0

SUB A #$50

168.000

BMI DT

169.000

170.000 ADD B #$30

171.000 DT STA B HMDTHD

172.000 +

173.000 *

174.000 *

ASL LIBTEM

175.000

ROL MSBTEM

176.000

ROL UNTTEN

177.000

ROL HNDTHD

178.000

179.000

DEX

BME REGIN

180.000

FIGURE 17 - 3%-Digit Dual Ramp Software (Page 3 of 5)

```

```

AND A #$08

241.000

ADD A #$34

242.000

STA'A PIAIBO

243.000

JMP RESTAR

244.000

245.000 *

246.000 *

LOOK-UP TABLE FOR BCD TO 7 SEGMENT

247.000 *

CONVERSION

248.000

DRG $0000

249.000

FCB $7E,$30,$6D,$79,$33,$5B,$5F,$70,$7F,$73

250.000

END

251.000

MON

252.000

```

FIGURE 17 - 3½-Digit Dual Ramp Software (Page 5 of 5)

#### 4½-Digit Dual Ramp Program

The microprocessor software for a 4½-digit dual ramp A/D is shown in Figure 19. This program in an extension of the 3½-digit A/D just discussed and has a full scale input voltage of 1.9999 volts. Due to the addition of the extra digit, a fourth PIA port for the 7-segment display is required. The PIA port configuration used for ramp control, comparator, etc. is identical to that used in the 3½-digit A/D.

The addition of the extra digit also implies a longer ramp up time period which is produced by increasing the initialization of the index register in line 115. This longer ramp up time period also requires the change of the extra count subtraction statements of lines 137 and 138 to

maintain the extra count subtraction of 10% ramp up time. Also, the longer ramp up time period will require a larger integration capacitor to prevent saturation of the MC1405 integrator. This is of course, assuming the same MPU clock frequency. The remainder of the A/D external hardware is unchanged except for the addition of the fourth full digital display. Figure 18a can be used for the 4½-digit A/D without modification, and Figure 18b can be used with only the addition of another digit.

The software for the binary-to-BCD converter remains the same for the 4½-digit A/D since it is capable of handling up to 16 bits. The conversion routine for BCD-to-7 segment code must be modified to handle the extra digit although the same basic technique is retained.

```

FIGURE 19 - 4½-Digit Dual Ramp Software (Page 1 of 5)

1.000

MAM DWA 30

2.000

OP'T MEM

3.000 *

4.000 *

5.000 *

6.000 *

7.000 *

4 1/2 DIGIT A/D

8.000 *

9.000 *

10.000 +

11.000 *

12.000 +

THIS CONVERTER USES A MC1405 IN CONJUNCTION WITH THE

MC6800 MPU TO PRODUCE A 4 1/2 DIGIT A/D.

13.000 *

DUAL RAMP METHOD OF A/D CONVERSION IS USED.

14,000 *

15.000 *

16.000 +

THE INPUTS TO THE MPU CONSIST OF

17.000 *

18.000 *

CYCLE SWITCH -LOCATED AT PIAIBD (PB1)

19.000 *

COMPARATOR

- LOCATED AT PIA1BD (P87)

20.000 *

21.000 *

THE DUTPUTS FROM THE MPU CONSIST OF

/22.000 ◆

23.000 *

RAMP CONTROL - LOCATED AT PIAIBD (PBO)

24.000 +

CONVERSION FINISHED - LOCATED AT PIASBD (PB1)

25.000 *

DVERRANGE

- LOCATED AT PIA1BD (PB2)

26.000 •

POLARITY

- LOCATED AT PIAIBD (PB6)

27.000 •

28.000 +

7 SEGMENT DUTPUT

29.000 *

- PIASBD

TEMS

30.000 •

HUMDREDS - PIASAD

31.000 *

THOUSANDS - PIASBD

32.000 •

TENS OF THOUSANDS OR HALF DIGIT -PIASBD (PB7)

33.000 *

34.000 *

THE BINARY ANSWER IS STORED AT MSB AND LSB

35.000 •

36.000 *

THE BCD AMSWER IS STORED AT UNTTEN, HNDTHD, TENTSD

37.000 *

THE AMALOG IMPUT FOR THE MC1405 MUST HAVE A 2 VOLT

38.000 *

39.000 *

MAXIMUM WHILE THE AUTOPOLARITY OUTPUT FROM THE MPU

40.000 *

MAY BE USED TO TOGGLE A RELAY TO PROVIDE NEGATIVE

IMPUT CAPABILITY FOR THE AZD

41.000 *

42.000 ★

43.000 *

44.000

45.000 DRS $0000

```

```

46.000 MSB RMB 1

47.000 LSB RMB 1

48.000 INDEX RMB 2

TEMP STORAGE OF BINARY ANSWER

49.000 MSBTEM RMB 1

50.000 LSBTEM RMB 1

51.000 +

52.000 +

53.000 *

54.000 DRG $0010

55.000 UNTTEN RMB 1

56.000 HMDTHD RMB 1

57.000 TENTSD RMB 1

58.000 *

59.000 +

60.000 DRG $4006

B SIDE, DATA REGISTER

B SIDE, CONTROL REGISTER

61.000 PIA1BD RMB 1

62.000 PIA1BC RMB 1

A SIDE, DATA REGISTER

63.000 PIA2AD RMB 1

A SIDE, CONTROL REGISTER

64.000 PIAZAC RMB 1

B SIDE, DATA REGISTER

65.000 PIA2BD RMB 1

66.000 PIA2BC RMB 1

B SIDE, CONTROL REGISTER

67.000 ORG $4010

A SIDE, DATA REGISTER

68.000 PIASAD RMB 1

A SIDE, CONTROL REGISTER

69.000 PIASAC RMB 1

B SIDE, DATA REGISTER

70.000 PIA3BD RMB 1

B SIDE, CONTROL REGISTER

71.000 PIA3BC RMB 1

72.000 *

73.000 +

74.000 *

PIA ASSEMBLY

75.000 +

76.000 ORG $0A00

77.000 CLR PIA1BC

78.000 CLR PIAZAC

79.000 CLR PIASBC

80.000 CLR FIAGAC

81.000 CLR PIA3BC

32.000 LDA A #$4D

83.000 STA A PIAIBD

REMAINING PIA'S ALL DUTPUTS

84.000 LDA A #$0FF

85.000 STA A PIASAD

STA A PIA2BD

86.000

87.000 STA A PIASAD

88.000 STA A PIA3BD

SETS PIA CONTROL REGISTER BIT 3 HIGH

89.000 LDA A #$34

90.000 STA A PIAIBC

91.000 STA A PIASAC

92.000 STA A PIA2BC

93.000 STA A PIA3AC

94.000 STA A PIASBO

95.000 *

FIRST TWO HEX DIGITS OF LOOK-UP

96.000 LDA A #$0C

TABLE ADDRESSES

97.000 STA A INDEX

98.000 *

BASIC A/D +

99.000 +

*******

100.000 *

101.000 *

INITIALIZATION

102.000 +

103.000 LDA A ≎∄04

104.000 STA A PIA1BD RC HIGH

105.000 START LDA A PIAIBD COMPARATOR TEST

FIGURE 19 - 4½-Digit Dual Ramp Software (Page 2 of 5)

```

25

```

106.000 BMI START

107.000 CYCLE1 LDA A #14

108.000 STA A PIAIBD CONVERSION READY AND RC HIGH

109.000 *

110.000 *

111.000 *

CYCLE TEST

112.000 CYCLE LDA A PIA1BD

113.000 AMD A $$02

114.000 BEQ CYCLE

115.000 RESTART LDX #84E20

INITIALIZATION FOR RAMP UP

116.000 +

TIMING

117.000 CLR PIA1BD RESET OVERRANGE, CONVERSION FINISHED AND SET RC LOW

118.000 COMP LDA A PIAIBD

COMPARATOR TEST

119.000 BPL COMP

120.000 *

RAMP UP TIMING CYCLE

121.000 RAMPUP LDA B #$04

122.000

DEX

123.000

BME RAMPUR

124.000 *

125.000 +

RAMP DOWN TIMING CYCLE

126.000 *

127.000 +

128.000 RAMPDN STA B PIA1BD

RC HIGH

129.000

INX

130.000

CPX #0000

DUMMY STATEMENT

LDA A PIAIRD COMPARATOR TEST

131.000

132.000

BMI RAMPDH

133.000 ◆

134.000 ♦

EXTRA COUNT SUBTRACTION

135.000

STX MSB

136.000

STX MSBTEM

137.000

LDA A MSB

138.000

SUB A #$04

EXTRA COUNT SUBTRACTION

139.000

BMI POLRY1

POLARITY TEST

140.000

STA A MSB

141.000

STA A MSBTEM

142.000 *

143.000 *

144.000 *

145.000 +

146.000 *

BINARY TO BCD +

147.000 *

COMMERTER

148.000 *

149.000 *

150.000

CLR UNTIEN

151.000

CLR HNDTHD

152.000

CLR TENTSD

153.000

LDX #$0010

154.000 BEGIN LDA A UNTTEN

155.000

THE

156.000

AND A #$OF

157.000

SUB A #$05

158.000

BMI AT

159.000

ADD B #$03

160.000 AT TBA

161.000

AND A #$OFO

162.000

SUB A #$50

163.000

BMI BT

164.000

ADD B #830

```

165.000 BT STA B UNTTEN

```

166.000 •

167.000

LDA A HNDTHD

168.000

THE

AND A #$0F

169.000

SUB A #$05

170.000

BMI CT

171.000

ADD B #$03

172.000

173.000 CT TBA

AND A #$0F0

174.000

SUB A #$50

175.000

BMI DT

176.000

ADD B #$30

177.000

178.000 DT STA B HNDTHD

179.000 *

LDA A TENTSD

180.000

TAB

181.000

SUB A #$05

182.000

BMI ET

183.000

184.000

ADD B #$03

185.000 ET STA B TEMTSD

186.000 *

187.000 +

188.000

- ASL LSBTEM

ROL MSBTEM

189.000

190.000

ROL UNTTEN

ROL HNDTHD

191.000

ROL TENTSD

192.000

DEX

193.000

194.000

BME BEGIN

195.000 *

196.000

BRA BCD

197.000 DVRNG1 BRA DVRNGE

198.000 BRA BCD

199.000 *

BRANCH PATCH

200.000 POLRY1 BRA POLARY

201.000 *

BOD TO 7 SEGMENT

202.000 *

CONVERTER

203.000 +

204.000 +

205.000 BCD LDA A UNTTEN

AND A #$OF

206.000

STA A INDEX+1

207.000

LDX INDEX

208.000

LDA A 0.X

209.000

STA A PIAZAD

210.000

LDA A UNTTEN

211.000

212.000

LSR A

213.000

LSR A

214.000

LSR A

LSR A

215.000

STA A INDEX+1

216.000

LDX INDEX

217.000

218.000

LDA A 0.X

STA A PIASBD

219.000

LDA A HMDTHD

220.000

AND A #50F

221.000

STA A INDEX+1

222.000

LDX INDEX

223.000

224.000

LDA A 0.X

STA A PIASAD

225.000

FIGURE 19 - 4½-Digit Dual Ramp Software (Page 4 of 5)

```

```

226.000

LDA A

HNDTHD

227.000

LSR

Ĥ

228.000

LSR A

229.000

LSR A

230.000

LSR A

STA A INDEX+1

231.000

232.000

LDX INDEX

233.000

LDA A 0.X

STA A PIASED

234.000

235.000

LDA A TENTSD

236.000

SUB A #$01

237.000

BLT

END

238.000

LDA A #$80

239.000

ADD A PIASED

240.000

STA A PIASED

241.000

END JMP CYCLE1

242.000

243.000 OVRMGE LDA A #%OD ; OVERRANGE,RC HIGH, CON F

244.000

STA A PIA1BD

245.000

LDA

H

##F3

246.000

STA A PIAZAD

247.000

STA A PIA2BD

248.000

STA A PIASAD

249.000

STA A PIASBD

250.000

JMP CYCLE

251.000

252.000

253.000 POLARY LDX #$0100

254.000 BR DEX

255.000

BHE BR

256.000

LDA A PIA1BC

257.000

COM A

258.000

AND A #$08

259.000

ADD A #334

260.000

STA A PIAIBO

261.000

JMP RESTAR

262.000

263.000

264.000

265.000

ORG $0000

266.000

FCB $7E,$30,$6D,$79,$33,$5B,$5F,$70,$7F,$73

267.000

EMI

268.000

MOM

```

FIGURE 19 - 4½-Digit Dual Ramp Software (Page 5 of 5)

#### **External Dual Ramp System**

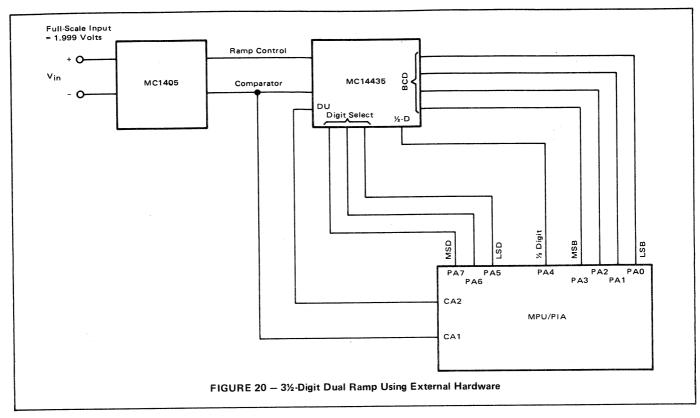

The final dual ramp A/D system to be discussed uses the MC1405 with an MC14435 CMOS dual ramp digital subsystem to provide a complete A/D converter external to the MPU system. This system provides an inexpensive A/D that is easily interfaced to an MPU system through a PIA and requires a minimum number of additional software instructions for control. Also, the microprocessor is available for performing other tasks during the A/D conversion.

When the MPU requires analog information, the data is brought into the MPU system through a PIA and placed

in memory for further use. The flow of this information is under control of the MPU system via an interrupt program. Figures 20 and 21 show the external devices with the MPU and the software instructions required to start the conversion and transfer the data from the A/D. Like the external successive approximation method described previously, this dual ramp technique reduces the number of MPU instructions required and increases the throughput of the overall MPU system. However, the increase in exterrnal hardware may offset these advantages. Also, additional external hardware is required for autopolarity and a 7-segment display.

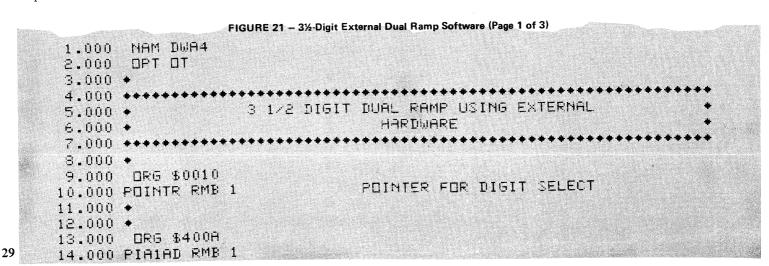

One port of a PIA is required for the interface to the MPU. The I/O configuration of this PIA is shown in lines 18 through 25 of the source program (Figure 21). The output of the MC14435 digital subsystem consists of three multiplexed BCD digits with the half digit output provided on a separate pin. The three most significant bits of the PIA port are connected to the digit select lines of the MC14435 while the four LSBs are connected to the BCD lines of the MC14435. The remaining PIA bit is connected to the half digit output. Lines 36 through 39 simulate the main MPU program which branches to the A/D subroutine starting in line 42. When this occurs the display update pin of the MC14435 (CA2) is set low which allows only the next data update to enter the MC14435 output latches. The wait for interrupt (WAI) instruction (line 44) stores the MPU stack and waits until the comparator output causes an interrupt on CA1.

At this point the processor is interrupted and vectored to the program beginning at line 50 causing it to demultiplex the BCD data on the output of the MC14435. The

least significant digit (LSD) is first selected by the pointer of lines 50 and 51. When a low condition on this LSD line occurs, the BCD data is stored via the indexed mode of addressing in memory location \$0100. The pointer is then shifted to the next position (line 57) and when the digit select line goes low the BCD data is stored in the next sequential memory location (\$0101). Then the MSD BCD value is placed in memory location \$0102 when the MSD digit select goes low. After the multiplexed BCD data has been placed in memory, the half digit is placed in memory location \$0103. At this point the display update line to the MC14435 is returned to a high position and the MPU returns from the interrupt and then from the subroutine back to the main program which requested the data.

A minimum of 183  $\mu$ s is required to transfer the A/D data to the MPU. This time period is dependent upon the A/D clock frequency which controls the digit select lines.

72.000

STA A 0,X

73.000 LDA A #\$30 74.000 STA A PIA1AC 75.000 RTI 76.000 + 77.000 + 78.000 + 79.000 MDN

FIGURE 21 - 3½-Digit External Dual Ramp Software (Page 3 of 3)

#### **SUMMARY**

Many MPU systems require analog information, which necessitates the use of an A/D converter in the microprocessor design. This note has presented two popular A/D techniques used in conjunction with the M6800 microprocessor system. These techniques, successive approximation and dual ramp, were shown using the MPU as the digital control element for the A/D system. This required dedication of the MPU to the A/D function during the conversion. Also shown were systems using the MPU to control the flow of data from an external A/D allowing the MPU to perform other tasks during the conversion.

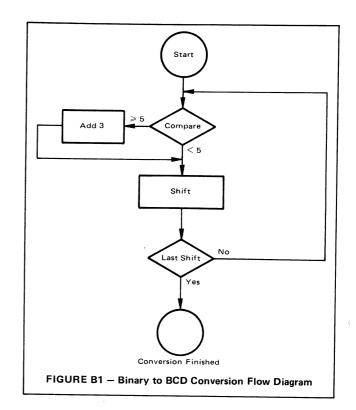

The variety of programs presented allow the designer to make a selection based upon hardware cost, conversion speed, memory locations and interrupt capability. Although the A/D programs shown here are complete designs, they are general designs and may be tailored to fit each individual application. Also a variety of digital outputs are available including binary, BCD, and 7-segment. In conjunction with the BCD output a 16-bit binary to BCD conversion routine is presented in Appendix B.

#### REFERENCES

Aldridge, Don: "Autopolarity Circuits for the MC1405 Dual-Slope A-D Converter System", EB-35, Motorola Semiconductor Products Inc.

Aldridge, Don: "Input Buffer Circuits for the MC1505 Dual Ramp A-to-D Converter Subsystem", EB-24, Motorola Semiconductor Products Inc.

Kelley, Steve: "4½-Digit DVM System Using the MC1505 Dual-Slope Converter", EB-36, Motorola Semiconductor Products Inc.

M6800 Microprocessor Applications Manual, Motorola Semiconductor Products Inc.

M6800 Microprocessor Programming Manual, Motorola Semiconductor Products Inc.

MC1505/1405 Data Sheet, Motorola Semiconductor Products Inc.

MC6800, MC6820 Data Sheets, M6800 Systems Reference and Data Sheets, Motorola Semiconductor Products Inc.

MC14435 Data Sheet, Motorola Semiconductor Products Inc.

#### APPENDIX A **MPU INSTRUCTIONS**

**Accumulator and Memory Instructions**

ADDRESSING MODES

BOOLEAN/ARITHMETIC OPERATION COND. CODE REG.

| 000047101-                  |              |          | MM |   |          | IRE |     | 1   | NDE |     | 1.  | XTI |     | 1        | MPLI   |            | (All register labels                                                       |       |          | 3   3  |                            |

|-----------------------------|--------------|----------|----|---|----------|-----|-----|-----|-----|-----|-----|-----|-----|----------|--------|------------|----------------------------------------------------------------------------|-------|----------|--------|----------------------------|

| OPERATIONS                  | MNEMONIC     | +        |    |   |          | ~   | #   | +   | ~   | #   | +   | ~   | #   | _        | ~      | #          | refer to contents)                                                         | H     | 11       | N Z    | z                          |

| Add                         | ADDA         | 8B       |    | 2 | 9B       | 3   | 2   |     | 5   | 2   | 1   | 4   | 3   |          |        |            | A + M → A                                                                  | 1 1   |          | - 1    | 1                          |

| Add Acmitrs                 | ADDB<br>ABA  | CB       | 2  | 2 | DB       | 3   | 2   | EB  | 5   | 2   | FB  | 4   | 3   |          | 2      |            | $B + M \rightarrow B$                                                      | 1 ' 1 |          |        | ‡                          |

| Add with Carry              | ADCA         | 89       | 2  | 2 | 99       | 3   | 2   | A9  | 5   | 2   | B9  | 4   | 3   | 1B       | 2      | 1          | $A + B \rightarrow A$ $A + B \rightarrow A$                                |       |          | - 1    | \$                         |

| ,                           | ADCB         | C9       | 2  | 2 | D9       | 3   | 2   | E9  | 5   | 2   | F9  | 4   | 3   |          |        |            | $B + M + C \rightarrow B$                                                  | 1:1   | •        | - 1    | ‡<br>‡                     |

| And                         | ANDA         | 84       | 2  | 2 | 94       | 3   | 2   | A4  | 5   | 2   | B4  | 4   | 3   |          |        |            | A · M → A                                                                  | 1 1   | •        | - 1    | ‡                          |

|                             | ANDB         | C4       | 2  | 2 | D4       | 3   | 2   | E4  | 5   | 2   | F4  | 4   | 3   |          |        |            | $B \cdot M \rightarrow B$                                                  |       | •        |        | - 1                        |

| Bit Test                    | BITA         | 85       | 2  | 2 | 95       | 3   | 2   | A5  | 5   | 2   | B5  | 4   | 3   | ĺ        |        |            | A·M                                                                        | 1 1   | •        | - 1    | . 1                        |

|                             | BITB         | C5       | 2  | 2 | D5       | 3   | 2   | E5  | 5   | 2   | F5  | 4   | 3   | ı        |        |            | В М                                                                        | 1 1   | •   1    |        | - 1                        |

| Clear                       | CLR          |          |    |   |          |     |     | 6F  | 7   | 2   | 7F  | 6   | 3   | İ        |        |            | 00 → M                                                                     | •     | •   F    | 3   S  | s                          |

|                             | CLRA         |          |    |   |          |     |     | l   |     |     | ĺ   |     |     | 4F       | 2      | 1          | 00 → A                                                                     | •     | •   F    | ≀   s  | s                          |

| C                           | CLRB         | ١.,      | _  |   | ١        | _   |     | l   | _   | _   |     |     |     | 5F       | 2      | 1          | 00 → B                                                                     | •     | •   F    | ≀∣s    | s                          |

| Compare                     | CMPA         | 81       | 2  | 2 | 91       | 3   | 2   | A1  | 5   | 2   | B1  | 4   | 3   | 1        |        |            | A - M                                                                      | •     | •   1    | ‡ ‡    | ¢                          |

| Compare Acmitrs             | CMPB<br>CBA  | C1       | 2  | 2 | D1       | 3   | 2   | E1  | 5   | 2   | F1  | 4   | 3   | ١        | _      |            | B – M                                                                      | •     | •   1    | - 1    |                            |

| Complement, 1's             | COM          | l        |    |   | ļ        |     |     | 63  | 7   | 2   | 72  |     | •   | 11       | 2      | 1          | A – B                                                                      | •     | •   ‡    |        |                            |

| oomproment, 1 s             | COMA         | l        |    |   |          |     |     | 63  | ′   | 2   | 73  | 6   | 3   | 1,2      | ,      |            | M → M                                                                      | •     | ₽∣₿      | 1.     |                            |

|                             | COMB         |          |    |   |          |     |     | İ   |     |     |     |     |     | 43<br>53 | 2      | 1          | Ā → A<br>Ē → p                                                             | 1 1   | •   ‡    |        | 1                          |

| Complement, 2's             | NEG          | l        |    |   |          |     |     | 60  | 7   | 2   | 70  | 6   | 3   | 53       | 2      | 1          | $ \begin{array}{c c} B \rightarrow B \\ 00 - M \rightarrow M \end{array} $ |       | 1        |        |                            |

| Negate)                     | NEGA         | l        |    |   |          |     |     | "   | •   | -   | '   | J   | J   | 40       | 2      | 1          | 00 - M → M<br>  00 - A → A                                                 |       | 1        | 1 1    |                            |

| -                           | NEGB         | 1        |    |   | 1        |     |     |     |     |     |     |     |     | 50       | 2      | 1          | 00 - A → A<br>00 - B → B                                                   |       | •   \$   |        |                            |

| Decimal Adjust, A           | DAA          |          |    |   | l        |     |     | l   |     |     |     |     |     | 19       | 2      | 1          | Converts Binary Add. of BCD Characters                                     |       | 1.       |        |                            |

|                             |              | l        |    |   | 1        |     |     |     |     |     |     |     |     |          | -      | •          | into BCD Format                                                            | 1 1   | *        | 1*     | 1                          |

| Decrement                   | DEC          | 1        |    |   |          |     |     | 6A  | 7   | 2   | 7A  | 6   | 3   |          |        |            | M − 1 → M                                                                  |       | 1        | 1      |                            |

|                             | DECA         |          |    |   | l        |     |     | 1   |     |     |     |     |     | 4A       | 2      | 1          | A – 1 → A                                                                  |       | 1        | 1      | ,                          |

|                             | DECB         | 1        |    |   |          |     |     |     |     |     |     |     |     | 5A       | 2      | 1          | B − 1 → B                                                                  |       | 1        | 1      |                            |

| xclusive OR                 | EORA         | 88       | 2  | 2 | 98       | 3   | 2   | A8  | 5   | 2   | В8  | 4   | 3   | ĺ        |        |            | A⊕M→A                                                                      |       | ۽ ا      | 1      |                            |

|                             | EORB         | C8       | 2  | 2 | D8       | 3   | 2   | E8  | 5   | 2   | F8  | 4   | 3   |          |        |            | $B \oplus M \rightarrow B$                                                 |       | 1        | 1      | 1                          |

| ncrement                    | INC          |          |    |   |          |     |     | 6C  | 7   | 2   | 7C  | 6   | 3   |          |        |            | M + 1 → M                                                                  |       | 1        | 1      | C                          |

|                             | INCA         |          |    |   |          |     |     |     |     |     |     |     |     | 4C       | 2      | 1          | A + 1 → A                                                                  | • •   | 1        | 1      | C                          |

| Load Acmitr                 | INCB         |          | •  | • |          |     |     | ١., | _   |     |     |     |     | 5C       | 2      | 1          | B + 1 → B                                                                  | •     | 1        | \$     | C                          |

| Luau Acmitr                 | LDAA         | 86       | 2  | 2 | 96       | 3   | 2   | A6  | 5   | 2   | B6  | 4   | 3   |          |        |            | $M \rightarrow A$                                                          | • •   | 1        | \$     | F                          |

| On Inclusion                | LDAB         | C6       | 2  | 2 | D6       | 3   | 2   | E6  | 5   | 2   | F6  | 4   | 3   |          |        |            | M → B                                                                      | •     | 1        | \$     | F                          |

| Or, Inclusive               | ORAA<br>ORAB | 8A       | 2  | 2 | 9A       | 3   | 2   | AA  | 5   | 2   | BA  | 4   | 3   |          |        |            | $A + M \rightarrow A$                                                      | • •   | 1        | 1      | F                          |

| Push Data                   | PSHA         | CA       | 2  | 2 | DA       | 3   | 2   | EA  | 5   | 2   | FA  | 4   | 3   |          |        |            | $B + M \rightarrow B$                                                      | • •   | \$       | 1      | F                          |

| usir Data                   | PSHB         |          |    |   |          |     |     |     |     |     |     |     | 1   | 36       | 4      | 1          | $A \rightarrow M_{SP}, SP - 1 \rightarrow SP$                              | •     | •        | •      | •                          |

| Pull Data                   | PULA         |          |    |   |          |     | ı   |     |     |     |     |     |     | 37<br>32 | 4<br>4 | 1          | $B \rightarrow M_{SP}, SP - 1 \rightarrow SP$                              | • •   | •        | •      | •                          |

|                             | PULB         |          |    |   |          |     |     |     |     | ł   |     |     |     | 33       | 4      | 1          | $SP + 1 \rightarrow SP, MSP \rightarrow A$                                 | •     | •        | •      | •                          |

| Rotate Left                 | ROL          |          |    | 1 |          |     |     | 69  | 7   | 2   | 79  | 6   | 3   | 33       | 7      | ۱ ۱        | $SP + 1 \rightarrow SP, M_{SP} \rightarrow B$ M)                           | •     | •        | •      |                            |

|                             | ROLA         |          |    |   |          |     | - 1 |     | •   | -   | , , | ٠   | ١   | 49       | 2      | 1          | A}                                                                         |       | \$       | \$     | 6                          |

|                             | ROLB         |          |    |   |          |     |     |     |     |     |     |     |     | 59       | 2      | 1          | B C 67 - 60                                                                |       | ‡<br>‡   | ‡<br>‡ | 6                          |

| Rotate Right                | ROR          |          |    |   |          |     |     | 66  | 7   | 2   | 76  | 6   | 3   |          |        | .          | M)                                                                         |       | <b>‡</b> | 1      | 6                          |

|                             | RORA         |          |    |   |          |     | ı   |     |     |     |     |     |     | 46       | 2      | 1          | A}                                                                         |       | 1        | 🕯      | 6                          |

|                             | RORB         |          |    |   |          |     | - 1 |     |     |     |     |     | -   | 56       | 2      | 1          | B) C b7 - b0                                                               |       | ‡        |        | 6                          |

| Shift Left, Arithmetic      | ASL          |          |    | - |          |     |     | 68  | 7   | 2   | 78  | 6   | 3   |          |        |            | M)                                                                         |       | 1        | 1      | 6                          |

| 1                           | ASLA         |          |    |   |          |     |     |     |     |     |     |     |     | 48       | 2      | 1          | A} 0 + 0111111-0                                                           |       | 1        | 1      | 6                          |

|                             | ASLB         |          |    |   |          |     |     |     |     |     |     |     | - 1 | 58       | 2      | 1          | B) C b7 b0                                                                 |       | 1        |        | 6                          |

| hift Right, Arithmetic      | ASR          |          |    |   |          |     |     | 67  | 7   | 2   | 77  | 6   | 3   |          |        |            | M)                                                                         | • •   | 1        | - 1    | 6                          |

|                             | ASRA         |          |    |   |          |     |     |     |     |     |     |     |     | 47       | 2      | 1          | A}                                                                         | • •   | \$       | \$ 0   | 6                          |

| hife Diahe 1                | ASRB         |          |    |   |          |     | -   | _   | _   |     |     |     | J   | 57       | 2      | 1          | B <b>b7 b0</b> C                                                           | •     | 1        |        | 6                          |

| hift Right, Logic           | LSR          |          |    |   |          |     | - 1 | 64  | 7   | 2   | 74  | 6   | 3   |          |        |            | M) -                                                                       | • •   | , ,      |        | 6                          |

|                             | LSRA         |          |    |   |          |     |     |     |     | - 1 |     |     |     | 44       | 2      | 1          | A 0                                                                        | •     |          |        | $\widecheck{\mathfrak{G}}$ |

| tore Acmitr.                | LSRB         |          |    |   | 0.7      | 4   |     |     | •   |     | 0.7 | _   |     | 54       | 2      | 1          | B b7 b0 C                                                                  | •     | R        |        | $\check{\mathfrak{G}}$     |

| tore Athlitt.               | STAA         |          |    |   | 97       | 4   | 2   | A7  | 6   | 2   |     | 5   | 3   |          |        |            | $A \rightarrow M$                                                          | •     | 1        | 1      | R                          |

| btract                      | STAB<br>SUBA | gΛ       | 2  | , | D7       | 4   | 2   | E7  | 6   | 2   |     | 5   | 3   |          |        |            | B → M                                                                      | • •   | 1        | 1      | R                          |

|                             | SUBB         | 80<br>C0 | 2  | 2 | 90<br>D0 | 3   | 2   | A0  | 5   | 2   |     | 4   | 3   |          |        |            | $A - M \rightarrow A$                                                      | • •   |          |        | \$                         |

| btract Acmitrs.             | SBA          | -00      | ۷. | 2 | D0       | 3   | 2   | EO  | 5   | 2   | F0  | 4   | 3   | 10       | 2      | . 1        | B – M → B                                                                  | • •   |          | - 1    | \$                         |

| btr. with Carry             | SBCA         | 82       | 2  | 2 | 92       | 3   | 2   | A2  | 5   | ,   | R2  | 1   | ,   | 10       | 2      | 1          | $A - B \rightarrow A$                                                      | •     |          |        | \$                         |

|                             | SBCB         | C2       |    | 2 | D2       | 3   | 2   |     |     | - 1 |     |     | 3   |          |        |            | $A - M - C \rightarrow A$                                                  | • •   |          | - 1    | ‡                          |

| ansfer Acmitrs              | TAB          | 02       | -  | - | J.2      | 5   | -   |     | J   | -   | F2  | 4   | 3   | 16       | 2      | ,          | $B - M - C \rightarrow B$                                                  | • •   |          | - 1    | ‡                          |

| · · · · · · · · · · · · · · | TBA          |          |    |   |          |     | 1   |     |     |     |     |     |     | 16<br>17 |        | 1          | A → B                                                                      | • •   |          | - 1    | R                          |

| est, Zero or Minus          | TST          |          |    |   |          |     |     | 6D  | 7   | 2   | 7D  | 6   | 3   | "        | 4      | 1          | B → A<br>M 00                                                              | •     |          |        | R                          |

|                             | TSTA         |          |    |   |          |     |     |     | •   | -   | , 5 | ,   | - 1 | 4D       | 2      | 1          | M - 00<br>A - 00                                                           | •     | - 1      | - 1    | R                          |

|                             | TSTB         |          |    |   |          |     |     |     |     |     |     |     | - 1 |          |        | i          | B - 00                                                                     | •     |          | - 1    | R                          |

|                             |              |          |    |   |          |     |     |     |     |     |     |     |     |          | -      | <u>. T</u> | 0 - 00                                                                     | • •   | \$       | 1      | R                          |

#### LEGEND:

- Operation Code (Hexadecimal);

- Number of MPU Cycles;

- Number of Program Bytes;

- Arithmetic Plus;

- Arithmetic Minus;

- Boolean AND;

- Boolean Inclusive OR;

- Boolean Exclusive OR;

- M Complement of M;

- Transfer Into;

- Bit = Zero;

- 00 Byte = Zero;

MSP Contents of memory location pointed to be Stack Pointer;

#### 0

$\textbf{Note} - \textbf{Accumulator} \ \textbf{addressing} \ \textbf{mode} \ \textbf{instructions} \ \textbf{are} \ \textbf{included} \ \textbf{in} \ \textbf{the} \ \textbf{column} \ \textbf{for} \ \textbf{IMPLIED} \ \textbf{addressing}$

#### CONDITION CODE SYMBOLS:

- Half-carry from bit 3;